Le CEA-Leti a présenté à la conférence ISSCC un processeurs multicoeurs à six chiplets utilisant une couche d’interposition active, avec à la clé des gains significatifs en termes de consommation, de bande passante et d’évolutivité.

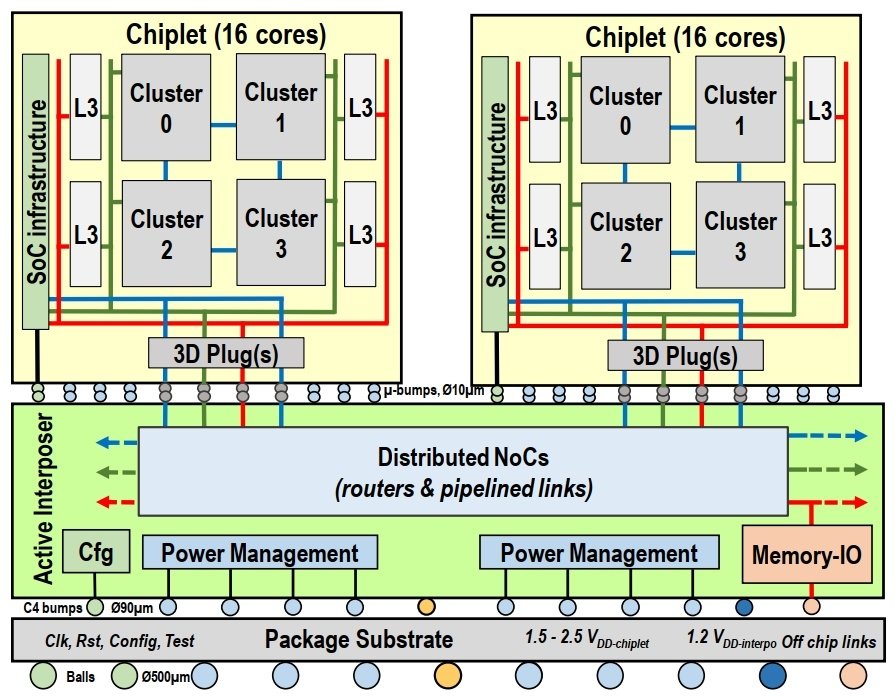

San Francisco – Le CEA-Leti a exposé lors de la conférence ISSCC une technologie originale de processeurs à chiplets reposant sur une couche d’interposition active, et non pas passive comme c’est généralement le cas. Le laboratoire de R&D grenoblois a développé un processeur à 96 cœurs répartis sur six chiplets FD-SOI 28nm, reposant sur une couche d’interposition Cmos 65nm assurant non seulement la connexion active entre les chiplets et avec les contacts externes du composant, mais aussi la gestion d’alimentation et le contrôle de mémoires.

Les liaisons de mémoire cache L1-L2 demeurent passives car à courte portée, mais les liaisons L2-L3 et entre le cache L3 et les mémoires extérieures bénéficient d’un réseau de routeurs/buffers répartis dans la couche d’interposition, ce qui permet de l’étendre à un grand nombre de chiplets et de l’utiliser pour des conceptions synchrones ou asynchrones.

La partie alimentation est assurée par des régulateurs à capacités commutées (un pour chaque chiplet), qui offrent un meilleur rendement que des régulateurs à faible chute de tention LDO. Au total, le composant délivre jusqu’à 220Gops à 1,15GHz ou 9,6Gops/W à 246MHz sous 0,6V.