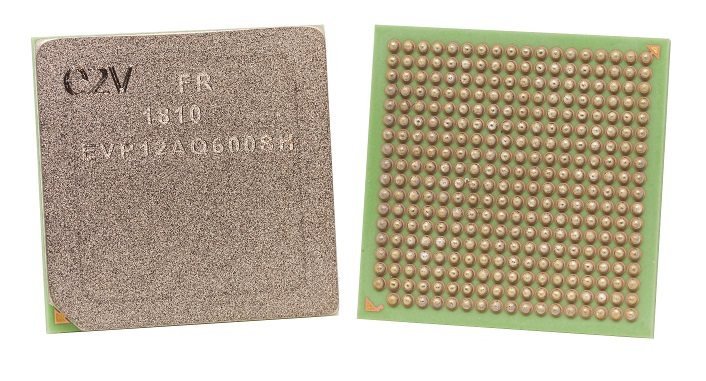

Teledyne e2v a trouvé un moyen d’augmenter de manière significative (jusqu’à 10dBFS) la marge dynamique SFDR de ses convertisseurs analogique-numérique EV12AQ600/605, lesquels délivrent jusqu’à 6,4Géch/s sur 12 bits en entrelaçant les échantillons des quatre cœurs de conversion A/N à 1,6Géch/s. Cette méthode repose sur l’algorithme de post-traitement ADX4 conçu par SP Devices, une société du groupe Teledyne. L’IP réduit dynamiquement les fréquences parasites résultant des différences de gain, d’offset et de phase entre les quatre coeurs. Une tâche qu’il devient difficile d’effectuer dans le domaine analogique pour des convertisseurs de plus de 10 bits, surtout à des fréquences dépassant le gigahertz. En pratique, le code ADX4 tourne sur le FPGA de post-traitement associé au convertisseur – il peut même être ajouté sur des montages déjà déployés.

Les CAN 12 bits 6,4Géch/s de Teledyne e2v gagnent 10dB de dynamique