Xilinx avait promis sa nouvelle génération de FPGA 20 nm UltraScale pour la fin de l’année 2013. L’américain a tenu sa promesse, les premières puces ayant été produites en novembre dernier (échantillonnage général début 2014) tandis que la documentation et la suite de conception Vivado sont désormais disponibles pour ces circuits programmables. Produits par TSMC, ces composants sont répartis entre les familles Kintex pour le milieu de gamme et Virtex pour le haut de gamme.

Les Kintex embarquent jusqu’à 1,16 million de cellules logiques, 5520 blocs DSP, 76 Mbits de Ram, des blocs d’émission-réception 16,3 Gbit/s en fond de panier et des interfaces PCIe Gen3, Ethernet 100 Gbit/s, Interlaken 150 Gbit/s et DDR4.

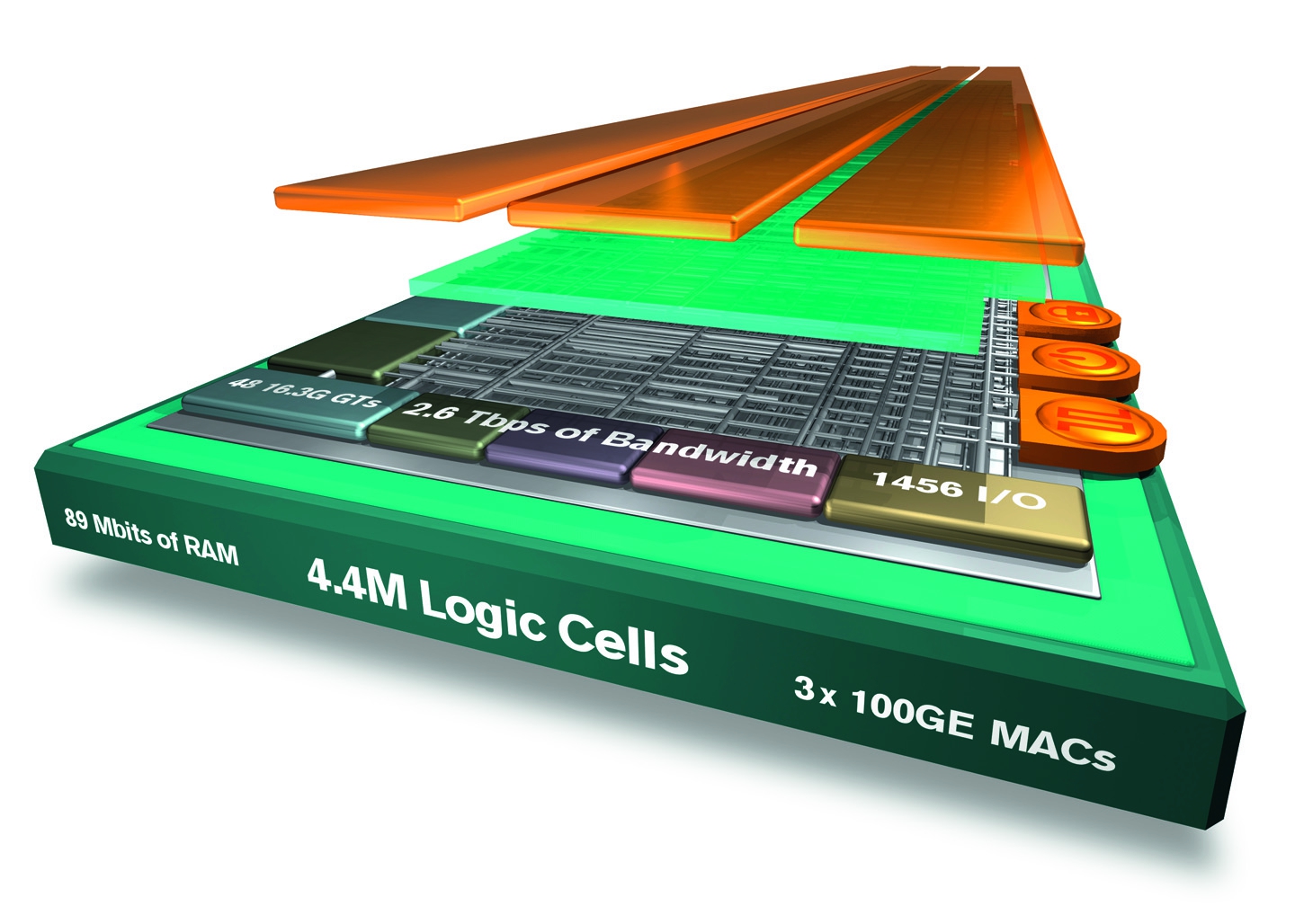

Par rapport à ce qui avait déjà été annoncé par l’américain cet été, la nouveauté réside surtout du côté des Virtex, en l’occurrence du mastodonte XCVU440 – qui, lui, sera échantillonné fin 2014. Reprenant en l’améliorant, notamment au niveau des vias traversants, l’architecture 3D du précédent Virtex-7 2000T, le VU440 comprend trois puces FPGA surmontant un circuit logique, l’ensemble équivalent à un Asic de 50 millions de portes selon Xilinx. Là où les Kintex misent surtout sur la capacité de calcul de type DSP, le haut de gamme Virtex vise plutôt les applications gourmandes en bande passante (prototypage et émulation de circuits spécifiques, informatique, test et à la mesure hautes performances), le VU440 gérant 2,6 Tbit/s en interne et disposant de 4,4 millions de cellules logiques, 89 Mbits de Ram, 3 interfaces MAC Ethernet 100 Gbit/s et 6 portes PCIe.

A découvrir dans le numéro de janvier de notre magazine “ElectroniqueS”.