Le japonais présente une technologie de mémoire Sram capable de passer dynamiquement d’un mode actif à un mode veille avec rétention de données tout en combinant rapidité et faible consommation.

Renesas Electronics vient de développer une technologie de mémoire Sram à faible consommation visant notamment les circuits spécifiques destinés à la santé, à la domotique et aux objets connectés. Basée sur une structure SOTB (silicon on thin BOX), cette mémoire est capable de passer dynamiquement d’un mode actif, durant lequel le processeur exécute des opérations de lecture et d’écriture, à un mode veille avec rétention de données.

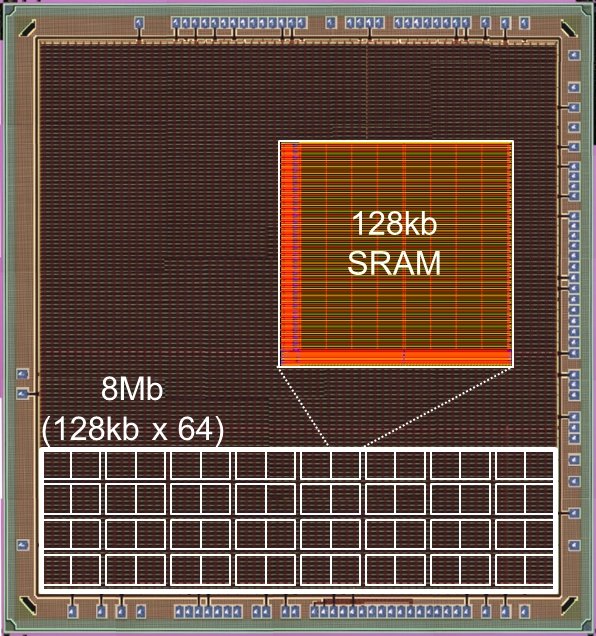

Les prototypes fabriqués en technologie 65nm présentent un délai de lecture de 1,84ns en mode actif et une consommation réduite à 13,7nW/Mbit en veille. Ils permettent d’éviter le recours à une mémoire non volatile interne ou externe au circuit pour stocker les données lorsque la Sram est en veille. Cette technologie a fait l’objet d’une présentation lors du Symposium VLSI qui se déroule actuellement à Kyoto.