Dotés de coeurs de processeurs, de blocs DSP, de convertisseurs de données rapides, d’interfaces très haut débit et/ou de mémoires avancées, les prochains FPGA en FinFET 7 nm de l’américain seront échantillonnés à la fin de l’année.

Baptisée ACAP (adaptive compute acceleration platform), la prochaine génération de FPGA de l’américain Xilinx poursuit résolument la vague de l’intégration croissante matérialisée par exemple dans ses derniers Zynq, en tâchant de conserver l’équilibre entre programmabilité et performances. L’objectif est d’offrir des performances multipliées par vingt pour les réseaux neuronaux par rapport aux FPGA Virtex VU9P 16nm, ou encore une bande passante quadruplée par rapport aux étages radio 16nm actuels pour les stations de base 5G.

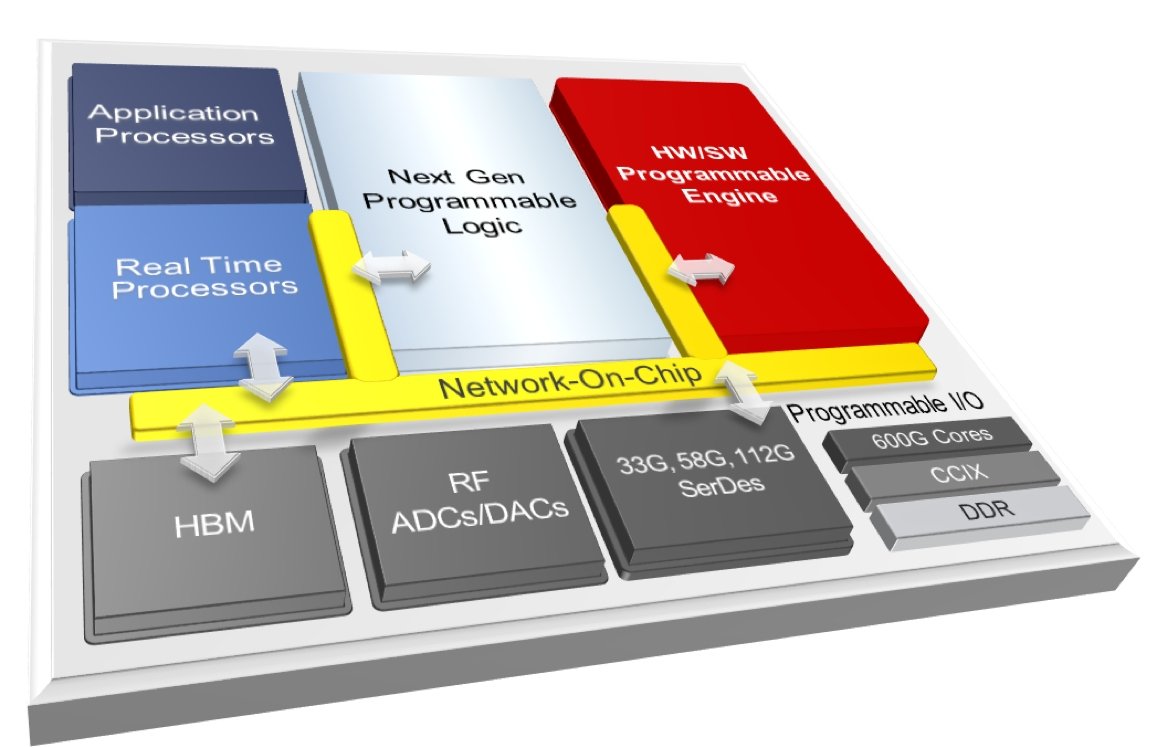

Programmée pour la technologie FinFET 7nm de TSMC, la première famille de FPGA ACAP (nom de code : Everest) mêlera donc logique programmable, DSP, processeurs d’applications, processeurs de traitement en temps réel, moteurs d’accélération programmables, convertisseurs A/N et N/A RF, interfaces Serdes 33G, 58G et, à l’avenir, 112G, et/ou mémoire HBM à large bande passante. Le tout sera relié par un réseau-sur-puce (network-on-chip ou NOC). Les premiers échantillons de circuits ACAP en 7nm sont attendus pour la fin de l’année 2018.