L’américain a validé sa technologie de logique programmable embarquée eFPGA sur le process 16 nm FinFET de TSMC.

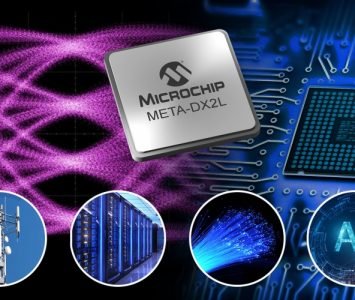

Achronix Semiconductor vient de valider la production de sa technologie de logique programmable embarquée Speedcore eFPGA sur le process FinFET 16nm de TSMC. L’IP d’Achronix permet d’ajouter de la mémoire embarquée, des blocs DSP et de 10.000 à 2.000.000 de tables LUT de logique programmable au sein d’un circuit spécifique ou d’un système sur une puce avec, selon l’américain, des gains en densité, en coût, en consommation et en performance par rapport aux FPGA autonomes.

La validation sur la technologie de production de TSMC a été effectuée à l’aide de la carte Speedcore16t, grâce à laquelle un utilisateur peut tester ses algorithmes à 500MHz avant de finaliser les caractéristiques du bloc Speedcore qu’il intègrera dans son circuit.